# TRANSDIMENSION

## **OTG243**

# Three Port, Single Chip USB On-The-Go Host/Function Controller

## **Description**

TransDimension's OTG243 is a single chip USB Host and Function controller that is the first of a family of integrated low-cost, high-performance, On-the-Go (OTG) controllers optimized and specifically designed for embedded systems, peripherals, mobile communication, and consumer products. It is a combination of a standard USB host controller and an OTG dual-role device controller. The OTG243 enables any embedded system to operate as a USB Host and a Function, thereby dramatically expanding the degree of interconnectivity and extending the applicability of the USB into many new areas. Software support for the OTG243 is available from SoftConnex Technologies, Inc., a wholly owned subsidiary of TransDimension Inc., and includes USBLink OTG Stack, ported to a wide variety of RTOSs, interface code to the OTG243 and USB device drivers. Peer-to-Peer connectivity is made simple with the OTG243 since USB connectivity is achieved without PC intervention. Applications include mobile and post-PC products such as cellular phone, palmtop PC, PDA, set top box, home gateway, and Internet appliances, to name a few. The OTG243 can operate in the following modes:

- USB On-the-Go dual-role device: One OTG port plus a standard USB host with two downstream ports

- Simultaneous standard USB host with two downstream ports and one USB function upstream port

- Standard USB host with three downstream ports

The host controller in the OTG243 is the only true transfer level embedded USB host and On-the-Go controller that can be interfaced directly to most popular microprocessors and easily programmable. The active endpoint and transfer descriptors are located in the on-chip memory, thus significantly reducing processor overhead relative to any comparable product on the market.

The full speed function controller is very flexible and software configurable, in terms of the active endpoint number (8), type, size, and buffering mechanism of each endpoint.

## **Features**

Concurrent operation of On-The-Go, Host and Function ports

- Fully compliant with USB On-the-Go specification and USB Specification Rev. 2.0 for full-speed (12Mb/s) and low-speed (1.5Mb/s) USB devices

- High-performance USB host: Full USB bandwidth utilization with low load on system microprocessor without bus mastering

- Transaction scheduling and transfer level protocol implemented in hardware including bandwidth management, data toggle and retry

- Guaranteed isochronous transfer with loose timing requirements on the microprocessor

- Fast microprocessor and dual-DMA interface access cycle (~25MB/s for 16-bit data bus, and ~50MB/s for 32-bit data bus)

- Double/multi buffering support for all four types of USB transfers

- Separate transfer descriptor and data memory space

- On-chip charge pump generates 5V power up to 12mA, capable of supporting more bus-powered devices than specified in the USB On-the-Go specification

- Capable of supporting up to 500mA to peripherals when using external 5V power supply while controlling an external charge pump

- Integrated on-chip pull-up and pull-down resistors

- Power saving mode for whole chip and host controller, and suspend mode for function controller

- Integrated PLL supports external crystal or crystal oscillators of 6MHz, 12MHz, 24MHz, and 48MHz

- Single 3.3V power supply, 3.3 V I/O (LVCMOS/TTL), 5 V tolerant

- Software and hardware Host Negotiation Protocol

- Session Request Protocol

- Direct interface to microprocessors, RISC, CISC, and DSP's including but not limited to x86, Intel XScale & StrongARM, Hitachi SH3, Fujitsu SPARCLite, NEC and Toshiba MIPS, ARM7, ARM9, Motorola PowerPC, ColdFire and Dragonball among others

- Embedded RTOS software available for WinCE, Linux, VxWorks, Nucleus, LynxOS, QNX, pSOS, PowerTV, SMX, AMX, ThreadX, VRTX, ITRON, Symbian OS and MS-DOS operating systems among others

- USB device driver software available including printer, speaker, mass storage, hub, modem, Ethernet, mouse, keyboard, digital camera, video camera, cell phone, STB, PDA, etc.

- Programmable DMA and IRQ polarities

- 100 pin LQFP and 84 ball TF-BGA packages available

## **Architecture**

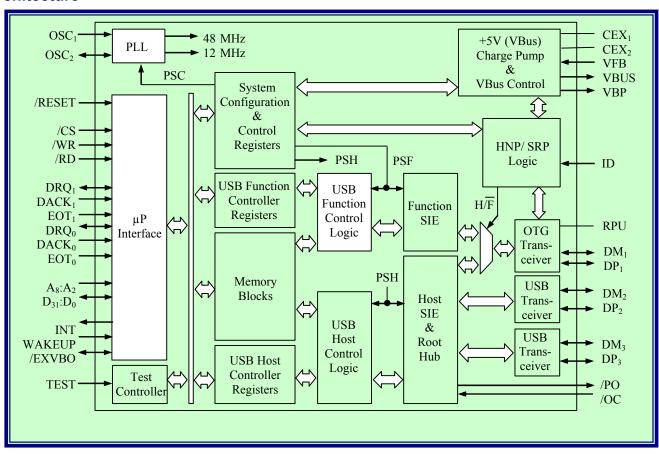

Figure 1 – OTG243 Architectural Block Diagram

**USB/OTG Host logic blocks:** The USB Host Controller Logic, the host Serial Interface Engine (SIE) and the root hub are responsible for the fully complaint (not reduced) USB host of the OTG243 - supporting transfer level user interface, scheduling/processing transactions, and monitoring/handling port events.

**USB/OTG Function logic blocks**: The USB Function Controller Logic, together with the function SIE, manages all low-level USB function protocols upon which a fully compliant full speed USB peripheral is operated.

**Direct Memory Access:** Two DMA channels allow fast data movement between the application and the OTG243 with minimum intervention from the microprocessor. Programmed accesses to the OTG243 through DMA and those through memory mapped, programmed I/Os can be interleaved.

**Interrupt Handling**: Interrupts from the OTG243 to a microprocessor are minimum, as an interrupt is generated only at the end of a USB transfer (for both host and function), which can have a size of up to 4 Mbytes\*. Moreover, an interrupt event may be delayed inside the OTG243, and be bundled with others to further reduce the number of interrupt occurrences.

<sup>\*</sup> Even though invisible to the high level software, low level interrupts are necessary to handle 4KByte internal data RAM.

**Memory blocks:** The Host Controller Logic, the Function Controller logic, the microprocessor, and the DMA logic are all entitled to have access to the memory blocks for data and control. A RAM Arbiter sequences all RAM access.

**Register banks:** There are 3 register banks used for System Configuration, Host Control, and Function Control.

**Host Negotiation Protocol (HNP):** The user may select one of two HNP types supported in the OTG243. The user simply selects software or hardware HNP, depending on their application, with each type of HNP having its own merits. Hardware HNP is a built-in state machine, which reduces microprocessor interrupts, whereas, software HNP is maintained and manipulated in the software space and provides an extra option to the user.

Both types of HNP, when enabled, will support negotiation with an attached OTG device, in order to determine in which role (A-device or B-device) the OTG243 will operate as, in a session. The OTG243 contains the required analog components (comparators, charge pump, etc.) and digital logic to support the operation. The microprocessor interfaced to the OTG243 can also disable this negotiation process, and configure the dual-role device port of the OTG243 to operate as a host or function. HNP may only be implemented in conjunction with a Mini-AB receptacle.

**Session Request Protocol (SRP):** The USB OTG specification is positioned to service mobile products that are battery powered. The SRP protocol allows the A-device to conserve power by turning the USB VBus signal off depending on whether there is USB traffic. The B-device will have the capability to initiate bus activity via SRP and hence the A-device device will be capable of responding to this via SRP. The OTG243 On-The-Go port fully complies to the SRP protocol as described and defined in the USB On-The-Go specification.

**Operational Modes:** The OTG243 can be operated in different modes via software configuration:

|               | Port 1   | Port 2 | Port 3 | Application                                                                                                                                                                                                        |

|---------------|----------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| On-The-Go     | OTG      | Host   | Host   | OTG application and two host ports                                                                                                                                                                                 |

|               |          |        |        | (concurrent OTG/Host operation supported. The OTG port may behave in either host or function modes and dynamically switch between roles through the HNP or when directed by a user change of USB cable connection) |

| Host Only     | Host     | Host   | Host   | Host only controller with three ports                                                                                                                                                                              |

| Host/Function | Function | Host   | Host   | Two host and one function port (concurrent host and function operation supported)                                                                                                                                  |

**5V charge pump:** The OTG243 charge pump generates +5 volts (VBUS) of up to 12mA from its 3.3V power supply. If an external 5V is available in the system, the internal OTG243 charge pump may be disabled, and the OTG243 will still be able to provide full control (switch on/off, pulsing, etc.) of the VBUS. There are several modes to consider when considering power:

**Microprocessor interface:** The OTG243 is a memory mapped device and can easily interface, gluelessly, to the system bus of most popular microprocessors, CISC, RISC and DSP's including but not limited to x86, Intel XScale & StrongARM, Hitachi SH3, Fujitsu SPARCLite, NEC and Toshiba MIPS, ARM7, ARM9, Motorola PowerPC, ColdFire and Dragonball, among others. Reference designs and evaluation boards for some of these processors are available with new designs being added and tailored to fit particular customer needs.

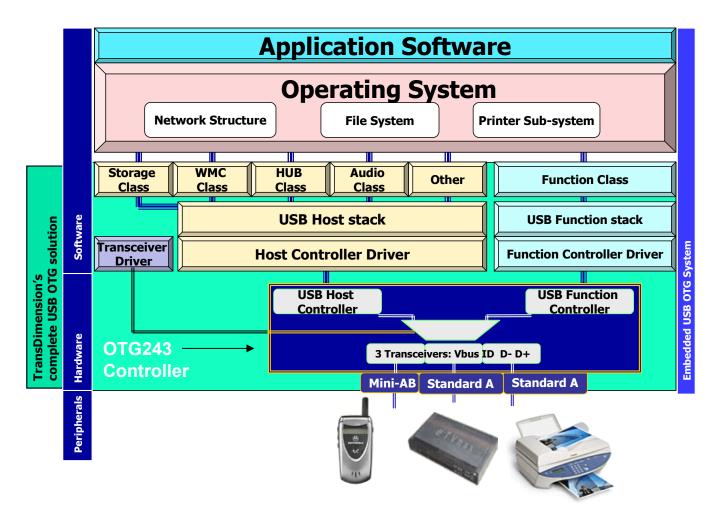

**Software support:** TransDimension is a leader in the USB embedded market, bringing both software and silicon to its customers. The company provides development and support packages and a wide spectrum of USB host and On-The-Go software support in C source code to reduce development cost and time to market for its customers. Software for a variety of operating systems is fully tested and supported to easily interoperate with the above listed microprocessors. TransDimension is a Microsoft Windows embedded partner.

TransDimension is a Microsoft Windows Embedded Partner (WEP) and supplies Host Controller Driver (HCD) Interface code to OTG243 for Linux and WinCE operating systems, as well as applicable USB class and device drivers for use in a wide variety of mobile and post-PC products.

For many other Real Time Operating Systems (RTOS) as listed previously, TransDimension and SoftConnex supply the USBLink On-The-Go software solution, which utilizes proven software technologies from SoftConnex's USBLink Host and USBLink Device software products, thereby providing a complete, integrated solution for USB On-The-Go applications.

Figure 2 – Software Stack and TransDimension's Complete USB OTG solution

## OTG243 Reference Designs, Evaluation/Demo Boards and Developer Kits

## **Reference Designs**

A growing number of designs are available with worldwide support from TransDimension. The current reference designs listed below include schematics, application notes and instructions on how to interface to the associated microprocessor of interest. In addition, software is available for specific operating systems including: WinCE, Linux, uCLinux, VxWorks, Nucleus, Lynx, QNX, Symbian OS, OS20, OS40, pSOS, PowerTV, SMX, ThreadX, VRTX, ITRON, MS-DOS operating systems. Contact your local TransDimension representative for ordering information of additional new reference designs for other microprocessors, CISC, RISC, and DSP's including Fujitsu SPARCLite, NEC and Toshiba MIPS, Motorola PowerPC, among others.

|   | OTG243 / Intel StrongARM        | USB On-The-Go Reference Design |

|---|---------------------------------|--------------------------------|

|   | OTG243 / Intel XScale (PXA250)  | USB On-The-Go Reference Design |

| • | OTG243 / Hitachi SH-3 / SH-4    | USB On-The-Go Reference Design |

|   | OTG243 / Motorola Dragonball    | USB On-The-Go Reference Design |

|   | OTG243 / Motorola ColdFire 5272 | USB On-The-Go Reference Design |

|   | OTG243 / ARM7                   | USB On-The-Go Reference Design |

#### **Evaluation / Demo Kits**

## EVB243: Evaluation Board with OTG243 silicon in LQFP package

The EVB243 is a small board (3.5"x3.5") that brings out all of the pins necessary to interface with microprocessors available on the market, today. The board has 3 USB receptacles (one USB OTG mini-AB and two standard USB host receptacles) ready to connect to any USB peripheral, hub or USB host. The main components on the EVB243 board consist of the OTG243 silicon in 100-pin LQFP, a microprocessor interface connector and Vbus distribution/manipulation electronic circuitry. Please see your local TransDimension sales representative for ordering information and specifications.

#### BGA243: Evaluation Board with OTG243 silicon in TF-BGA package

The BGA243 board has the same features as the EVB243 evaluation board with the exception of the package type of the OTG243 silicon on the board. This board may be used by customers to evaluate the technology using TF-BGA packaging.

## PCE243: PCI card with OTG243 silicon in LQFP package

The PCE243 card and associated documentation contains everything you need to perform an evaluation of the functionality and development on the OTG243 chip, in a PCI bus environment. The PCE243 card is a standard PCI card that may be inserted into any PCI slot, inside a personal computer or laptop docking station.

OTG243 / PCI USB On-The-Go Evaluation card

The PCE243 card may be used in any 33 MHz PCI system. The PCE243 will automatically adjust to a 3.3V or 5V PCI environment. The PCE243 PCI card quickly allows customers to start developing software around the OTG243 controller. Once the PCE243 card has been installed, the user will gain access to all of the development software kits available with the chosen operating system. TransDimension will supply the drivers necessary to evaluate the PCE243 PCI card in both OTG and Host mode simultaneously, in the Microsoft MS-DOS based operating systems and Linux operating systems.

The PCE243 card has three USB receptacles (one USB OTG mini-AB and two standard USB host receptacles) supporting connectivity between the PCI based system and USB peripherals, hubs and other USB hosts. Please see your local TransDimension sales representative for ordering information and specifications.

## **USB On-The-Go Developer Kits**

TransDimension in partnership with various leading development platform vendors has made available a number of different and complete USB OTG "Developer Kits" dedicated for use by USB OTG embedded product designers and architects. These are TransDimension's first USB OTG Developer Kits found on the market specific to a number of popular processors used by leading retail vendors of mobile and post-PC products. In conjuction with easy-to-use software, the developer may accurately test and rate the performance, features and capabilities of the OTG243 as mapped to a specific processor under a specific operating system and associated USB device and class drivers. All associated software is developed in conjuction with SoftConnex, a subsidiary of TransDimension and leader in USB Software technology and supplier to many other USB chipset vendors.

- OTG243 / Intel XScale (PXA250) / WinCE Developer Kit

- OTG243 / Intel XScale (PXA250) / Linux Developer Kit

- OTG243 / Intel StrongARM SA1110 / WinCE Developer Kit

- OTG243 / Intel StrongARM SA1110 / Linux Developer Kit

- OTG243 / Motorola ColdFire 5272 / uCLinux Developer Kit

- OTG243 / Sharp LH79520 ARM720T / Linux Developer Kit

The above Developer Kits include an evaluation card/module (namely: AXB243, IXB243, CXB243 or A7B243) designed, supplied, sold and supported by TransDimension. The specific development platforms are designed, supplied, sold and supported by different vendors including Accelent Systems, Inc., Intrinsyc Software Inc., SHARP Inc., and Arcturus Networks Inc. More vendors will be added as other Development kits become available.

Each Development kit consists of the following:

- OTG243 data sheet

- Evaluation card/module schematics in pdf and/or Orcad format

- Reference design document for OTG243 and the specific CPU

- One evaluation card/module

- Developer kit User Guide

- OTG243 interface software in object format

- Contact information to obtain development platforms for specific vendors (eq. Arcturus networks, etc.)

#### Evaluation card/module hardware features:

- One OTG port and two Host ports

- OTG port can be configured to be Host only, Function only, or OTG only

- Direct connect to the expansion bus of vendor specific development platform

- I/O access (16-bit and/or 32-bit data, 7-bit address, CS, WR, RD and INT signals)

## Evaluation card/module software features:

Choice of OTG243 interface code under WinCE 3.0/.NET or Linux (variety of kernel versions) to USB host stack, device stack and OTG transceiver driver in object format specific to the development platform and CPU

For other RTOS (VxWorks, Nucleus, Symbian OS, MS-DOS, ThreadX, etc.) USB software support, TransDimension in conjunction with SoftConnex Technologies, a subsidiary of TransDimension, offers USBLink USB stack and a variety of USB class and device drivers.

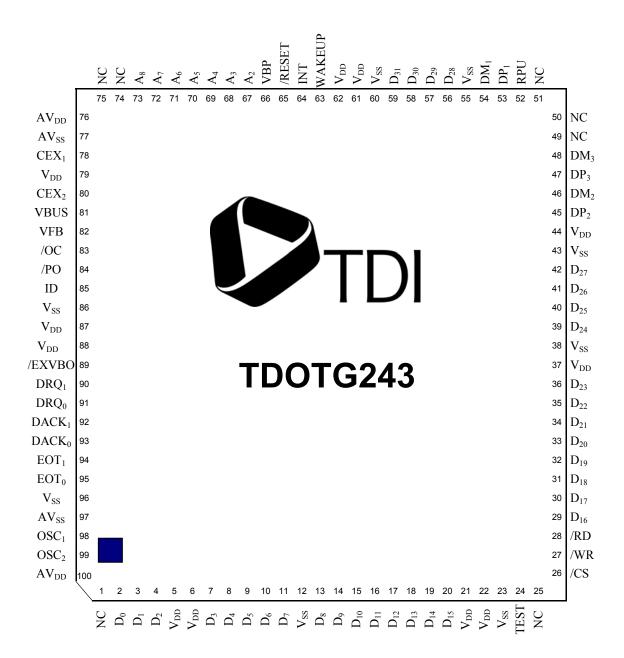

# **Pin Descriptions and Packaging**

| Pin<br>No. | Pin Name         | Pin<br>No. | Pin Name          |

|------------|-----------------|------------|-----------------|------------|-----------------|------------|------------------|------------|-------------------|

| 1          | NC              | 21         | $V_{DD}$        | 41         | D <sub>26</sub> | 61         | $V_{DD}$         | 81         | VBUS              |

| 2          | D <sub>0</sub>  | 22         | $V_{DD}$        | 42         | D <sub>27</sub> | 62         | $V_{DD}$         | 82         | VFB               |

| 3          | D <sub>1</sub>  | 23         | V <sub>SS</sub> | 43         | V <sub>SS</sub> | 63         | WAKEUP           | 83         | /OC               |

| 4          | D <sub>2</sub>  | 24         | TEST            | 44         | $V_{DD}$        | 64         | INT              | 84         | /PO               |

| 5          | $V_{DD}$        | 25         | NC              | 45         | DP <sub>2</sub> | 65         | /RESET           | 85         | ID                |

| 6          | $V_{DD}$        | 26         | /CS             | 46         | DM <sub>2</sub> | 66         | VBP              | 86         | V <sub>SS</sub>   |

| 7          | $D_3$           | 27         | /WR             | 47         | DP <sub>3</sub> | 67         | A <sub>2</sub>   | 87         | $V_{DD}$          |

| 8          | D <sub>4</sub>  | 28         | /RD             | 48         | DM <sub>3</sub> | 68         | $A_3$            | 88         | $V_{DD}$          |

| 9          | $D_5$           | 29         | D <sub>16</sub> | 49         | NC              | 69         | $A_4$            | 89         | /EXVBO            |

| 10         | D <sub>6</sub>  | 30         | D <sub>17</sub> | 50         | NC              | 70         | A <sub>5</sub>   | 90         | DRQ <sub>1</sub>  |

| 11         | D <sub>7</sub>  | 31         | D <sub>18</sub> | 51         | NC              | 71         | A <sub>6</sub>   | 91         | $DRQ_0$           |

| 12         | V <sub>SS</sub> | 32         | D <sub>19</sub> | 52         | RPU             | 72         | A <sub>7</sub>   | 92         | DACK <sub>1</sub> |

| 13         | D <sub>8</sub>  | 33         | D <sub>20</sub> | 53         | DP <sub>1</sub> | 73         | A <sub>8</sub>   | 93         | DACK <sub>0</sub> |

| 14         | D <sub>9</sub>  | 34         | D <sub>21</sub> | 54         | DM <sub>1</sub> | 74         | NC               | 94         | EOT <sub>1</sub>  |

| 15         | D <sub>10</sub> | 35         | D <sub>22</sub> | 55         | V <sub>SS</sub> | 75         | NC               | 95         | EOT <sub>0</sub>  |

| 16         | D <sub>11</sub> | 36         | D <sub>23</sub> | 56         | D <sub>28</sub> | 76         | $AV_DD$          | 96         | V <sub>SS</sub>   |

| 17         | D <sub>12</sub> | 37         | $V_{DD}$        | 57         | D <sub>29</sub> | 77         | AV <sub>SS</sub> | 97         | AV <sub>SS</sub>  |

| 18         | D <sub>13</sub> | 38         | V <sub>SS</sub> | 58         | D <sub>30</sub> | 78         | CEX <sub>1</sub> | 98         | OSC <sub>1</sub>  |

| 19         | D <sub>14</sub> | 39         | D <sub>24</sub> | 59         | D <sub>31</sub> | 79         | $V_{DD}$         | 99         | OSC <sub>2</sub>  |

| 20         | D <sub>15</sub> | 40         | D <sub>25</sub> | 60         | V <sub>SS</sub> | 80         | CEX <sub>2</sub> | 100        | $AV_{DD}$         |

Figure 3 - OTG243 pin assignment for the 100-pin LQFP package

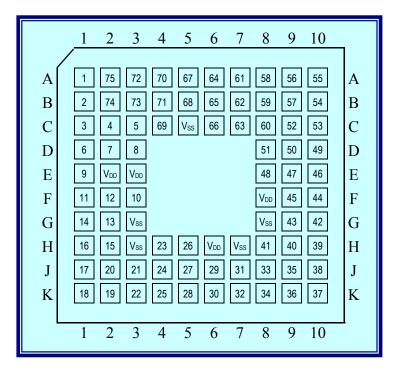

Figure 4 - OTG243 100-pin LQFP package (top view)

|    | Pin<br>Locatio<br>n | Pin<br>Name     |    | Pin<br>Locatio<br>n | Pin<br>Nam<br>e |    | Pin<br>Locatio<br>n | Pin<br>Name      |    | Pin<br>Locatio<br>n | Pin<br>Name       |

|----|---------------------|-----------------|----|---------------------|-----------------|----|---------------------|------------------|----|---------------------|-------------------|

| 1  | A1                  | D <sub>0</sub>  | 22 | K3                  | D <sub>17</sub> | 43 | G9                  | D <sub>31</sub>  | 64 | A6                  | ID                |

| 2  | B1                  | D <sub>1</sub>  | 23 | H4                  | D <sub>18</sub> | 44 | F10                 | WAKEUP           | 65 | B6                  | /EXVBO            |

| 3  | C1                  | D <sub>2</sub>  | 24 | J4                  | D <sub>19</sub> | 45 | F9                  | INT              | 66 | C6                  | DRQ <sub>1</sub>  |

| 4  | C2                  | $D_3$           | 25 | K4                  | D <sub>20</sub> | 46 | E10                 | /RESET           | 67 | A5                  | $DRQ_0$           |

| 5  | C3                  | D <sub>4</sub>  | 26 | H5                  | D <sub>21</sub> | 47 | E9                  | VBP              | 68 | B5                  | DACK <sub>1</sub> |

| 6  | D1                  | D <sub>5</sub>  | 27 | J5                  | D <sub>22</sub> | 48 | E8                  | A <sub>2</sub>   | 69 | C4                  | DACK <sub>0</sub> |

| 7  | D2                  | D <sub>6</sub>  | 28 | K5                  | D <sub>23</sub> | 49 | D10                 | $A_3$            | 70 | A4                  | EOT <sub>1</sub>  |

| 8  | D3                  | D <sub>7</sub>  | 29 | J6                  | D <sub>24</sub> | 50 | D9                  | A <sub>4</sub>   | 71 | B4                  | EOT <sub>0</sub>  |

| 9  | E1                  | D <sub>8</sub>  | 30 | K6                  | D <sub>25</sub> | 51 | D8                  | A <sub>5</sub>   | 72 | A3                  | AV <sub>SS</sub>  |

| 10 | F3                  | D <sub>9</sub>  | 31 | J7                  | D <sub>26</sub> | 52 | C9                  | A <sub>6</sub>   | 73 | B3                  | OSC <sub>1</sub>  |

| 11 | F1                  | D <sub>10</sub> | 32 | K7                  | D <sub>27</sub> | 53 | C10                 | A <sub>7</sub>   | 74 | B2                  | OSC <sub>2</sub>  |

| 12 | F2                  | D <sub>11</sub> | 33 | J8                  | DP <sub>2</sub> | 54 | B10                 | A <sub>8</sub>   | 75 | A2                  | $AV_{DD}$         |

| 13 | G2                  | D <sub>12</sub> | 34 | K8                  | DM <sub>2</sub> | 55 | A10                 | $AV_{DD}$        | 76 | E2                  | $V_{DD}$          |

| 14 | G1                  | D <sub>13</sub> | 35 | J9                  | DP <sub>3</sub> | 56 | A9                  | $AV_{SS}$        | 77 | E3                  | $V_{DD}$          |

| 15 | H2                  | D <sub>14</sub> | 36 | K9                  | DM <sub>3</sub> | 57 | B9                  | CEX <sub>1</sub> | 78 | F8                  | $V_{DD}$          |

| 16 | H1                  | D <sub>15</sub> | 37 | K10                 | RPU             | 58 | A8                  | $V_{DD}$         | 79 | H6                  | $V_{DD}$          |

| 17 | J1                  | TEST            | 38 | J10                 | DP <sub>1</sub> | 59 | B8                  | CEX <sub>2</sub> | 80 | C5                  | V <sub>SS</sub>   |

| 18 | K1                  | /CS             | 39 | H10                 | DM <sub>1</sub> | 60 | C8                  | VBUS             | 81 | G3                  | $V_{SS}$          |

| 19 | K2                  | /WR             | 40 | H9                  | D <sub>28</sub> | 61 | A7                  | VFB              | 82 | G8                  | V <sub>SS</sub>   |

| 20 | J2                  | /RD             | 41 | H8                  | D <sub>29</sub> | 62 | B7                  | /OC              | 83 | НЗ                  | V <sub>SS</sub>   |

| 21 | J3                  | D <sub>16</sub> | 42 | G10                 | D <sub>30</sub> | 63 | C7                  | /PO              | 84 | H7                  | V <sub>SS</sub>   |

Figure 5 - OTG243 84-ball TF-BGA pin assignment

Figure 6 - OTG243 84-ball TF-BGA package (top view)

# **Signal/Pin Descriptions**

The following shorthand notations are used to indicate the type of a signal/pin:

| l:  | input                                               | O: output           |

|-----|-----------------------------------------------------|---------------------|

| IO: | bi-directional                                      | OD: open drain      |

| PW: | power/ground                                        | PS: passive         |

| H:  | active high                                         | L: active low       |

| PL: | active level programmable but default to active low | N/A: not applicable |

| Pin<br>Name      | Signal<br>Type | Active<br>Level | Pin/Signal Description                                                                                                                                                                                                                                                                  |

|------------------|----------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC <sub>1</sub> | I              |                 | A passive crystal is connected across the two pins ( $OSC_1$ and $OSC_2$ ). A crystal oscillator output should be tied to $OSC_2$ . Upon power-on or hardware reset, $DRQ_1$ and $DRQ_0$ indicate the frequency of the crystal or crystal oscillator, which can be 6, 12, 24 or 48 MHz. |

| OSC <sub>2</sub> | Ю              |                 | As above.                                                                                                                                                                                                                                                                               |

| /RESET           |                | L               | Hardware reset – active low.                                                                                                                                                                                                                                                            |

| /WR I L Write strobe – active low.  /RD I L Read strobe – active low.  A <sub>8</sub> :A <sub>2</sub> I 7 bit address bus for an addressing space of 512 bytes.                                                                                                                              |                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

|                                                                                                                                                                                                                                                                                              |                               |

| A <sub>8</sub> :A <sub>2</sub> I 7 bit address bus for an addressing space of 512 bytes.                                                                                                                                                                                                     |                               |

|                                                                                                                                                                                                                                                                                              |                               |

| D <sub>31</sub> :D <sub>0</sub> IO 32-bit data bus. D <sub>31</sub> :D <sub>16</sub> should be pulled down with resistors but not tied directly to Vss, for 16-bit mode.                                                                                                                     | (15K ohm)                     |

| This is an output to switch the external 5V for OTG operation (0: VBUS on).  At POR (power-on-reset) or hardware reset the value of this p determine the width of the data bus (1: 32 bits; 0: 16 bits). If the floating, 32-bit bus is assumed. See Note 2.                                 | in will                       |

| DRQ <sub>1:</sub> DRQ <sub>0</sub> IO  Sensed at POR and hardware reset (/RESET) to determine the of the crystal or the crystal oscillator (00: 6 MHz; 01: 12 MHz; 11: 48 MHz). After that, they are outputs to MCU for DMA required two DMA channels. See Note 2 & 3.                       | 10: 24 MHz;                   |

| DACK <sub>1</sub> , DACK <sub>0</sub> I  DMA acknowledgement from the MCU for the two DMA channel levels are software programmable. See Note 3.                                                                                                                                              | iels. Active                  |

| EOT <sub>1</sub> , EOT <sub>0</sub> I  DMA end of transfer from the MCU for the two DMA channels levels are software programmable. See Note 3.                                                                                                                                               | Active                        |

| TEST I H Factory test mode – active high. This pin should be grounded operation.                                                                                                                                                                                                             | for normal                    |

| /PO O L When asserted, this indicates to turn on the gang power for al active low.                                                                                                                                                                                                           | host ports –                  |

| /OC I Over current condition indicator for gang powered host ports –                                                                                                                                                                                                                         |                               |

| INT O/OD PL Interrupt to the MCU. This pin can be software configured as open drain (OD) output. This pin is software programmable. (default). See Note 3.                                                                                                                                   |                               |

| WAKEUP  I  H  Wakeup the function/OTG controller in suspend mode – active                                                                                                                                                                                                                    |                               |

| Connected to the ID pin of the mini-AB connector (Port 1) for 0 applications. With the help of an internal pull-up resistor, it de chip's responsibility in an OTG application, (0: A-Device, 1: B-                                                                                          | termines the                  |

| DM <sub>1</sub> , DP <sub>1</sub> IO  Data lines for Port 1, which may serve as a host, function or O not used, these two pins can be left floating since the chip has down resistors.                                                                                                       |                               |

| Data lines for Port 2, a dedicated host port. If not used, each pulled down with a 15K resistor.                                                                                                                                                                                             | pin should be                 |

| DM <sub>3</sub> , DP <sub>3</sub> IO  Data lines for Port 3, a dedicated host port. If not used, each pulled down with a 15K resistor.                                                                                                                                                       | pin should be                 |

| CEX <sub>1</sub> , CEX <sub>2</sub> PS A 0.47 μF capacitor is connected across these two pins to sup internal charge pump circuit. If the internal charge pump is no two pins may be left unconnected.                                                                                       |                               |

| VBUS  PW  Serving as the A-device in an OTG application, this is the 5V of internal charge pump (when it is enabled), or the external VBu the VBus power from the attached DRD (dual role device) whi an OTG B-device. This pin should be left unconnected when F used for OTG applications. | is power. It is le working as |

| VFB I This pin is used in an external circuit to provide voltage feedba                                                                                                                                                                                                                      | ack for the                   |

|                  |    |   | internal charge pump which generates Vbus.                                                                                                                                                                                                                                                             |

|------------------|----|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VBP              | 0  | Н | VBus pulsing control. It is only useful when Port 1 is an OTG port for a B-device, and the internal VBus charge pump is disabled.                                                                                                                                                                      |

| RPU              | PS |   | An internal pull-up resistor on the DP <sub>1</sub> line currently exists. This internal resistor may be disabled via software. An external 1.5k $\Omega$ +/-1% resistor may be connected across this pin and DP1 for the OTG port only. If not used, this pin may be left floating. See Note 1 below. |

| AV <sub>DD</sub> | PW |   | Analog +3.3V.                                                                                                                                                                                                                                                                                          |

| AV <sub>SS</sub> | PW |   | Analog ground.                                                                                                                                                                                                                                                                                         |

| V <sub>DD</sub>  | PW |   | Digital +3.3V.                                                                                                                                                                                                                                                                                         |

| V <sub>SS</sub>  | PW |   | Digital ground.                                                                                                                                                                                                                                                                                        |

| NC               | PS |   | No connection. These pins must be left floating.                                                                                                                                                                                                                                                       |

Figure 7 - Detailed Pin Descriptions

## Note:

- Pins /EXVBO, DRQ<sub>1</sub> and DRQ<sub>0</sub> have multiplexed functions. They are inputs at power on or hardware reset to determine system configuration parameters - /EXVBO for the width of the data bus, and the other two for the frequency of the crystal or crystal oscillator. After reset, they are outputs assuming responsibilities suggested by their respective signal names.

- 2. The active levels for several pins (DRQ<sub>1</sub>, DRQ<sub>0</sub>, DACK<sub>1</sub>, DACK<sub>0</sub>, EPOT<sub>1</sub>, EOT<sub>0</sub>, and INT) are programmable by software but default to active low after power on or hardware reset. This feature allows glue-less interfacing with most microprocessors. Caution must be taken in user software to make sure relevant operations (DMA and/or interrupt) are disabled before alterations to default active levels are made.

- 3. When not used, pins are pulled-up, pulled-down or left floating. Consult the Chapter on hardware and software interfacing consideration for details.

- 4. The RPU pin allows the use of an external 1.50K± 1% resistor for developing USB applications that must comply with legacy specifications

## OTG243 USB On-The-Go Application Scenarios

#### Connect a Cellular phone to:

- a cellular phone to transfer directories, songs, files

- a PDA to exchange files, surf the web

- a digital camera to upload pictures to the web

- an MP3 player to exchange songs

- a scanner to scan business cards

- a portable hard disk to upload/download/broadcast music

#### Connect a Digital Camera to:

- a digital camera to exchange pictures

- a cellular phone to upload pictures to web

- a printer to print pictures

- a STB to view photos on a Television set

## Connect an MP3 player to:

- an MP3 player to exchange songs

- a CD player to upload songs

- a USB speaker to play songs

- a portable hard disk to upload/download songs

## **Connect a Personal Computer to:**

- a cellular phone to synchronize/broadcast data, MP3 files

- a PDA to synchronize data, transfer files

- a digital camera to upload pictures and email out

- a portable hard disk to store data

- an MP3 player to upload/download songs

## Connect a Digital Video Recorder to:

- a cellular phone to transfer directories, songs, files

- a PDA to exchange files, surf the web

- a digital camera to upload pictures to the web

## Connect a logic analyzer to:

- a cellular phone to broadcast data

- a PDA to transfer data

- a digital camera to download waveforms

- a printer to print waveforms

- a projector to project onto a screen for anlysis

## Connect a PDA to:

- a keyboard for user interface

- a PDA to exchange files

- a digital camera to upload/download pictures

- a portable disk drive to upload/download/store files

- a printer to print files

- a cellular phone to upload/download files

- an MP3 player upload/download files

## Connect a Portable Hard Disk to:

- a digital video recorder to store video clips

- an MP3 player to store songs

- a digital camera to store pictures

Connect a CarKit (AutoPC) to: (next revision of silicon will support Carkit Spec.)

- an MP3 player to play songs over a stereo connection

- a cellular phone to enable handsfree telephone operation,

- download latest phone list to your car

"All of these connectivity solutions are possible via the OTG port of the OTG243 chip, and yet there are still two more ports left for connectivity to standard USB devices and hubs!"

## **Applicable Documents and Specifications**

- □ On-The-Go supplement to the USB 2.0 specification, Revision 1.0, Dec 18, 2001. URL Link: <a href="http://www.usb.org/developers/data/otg1">http://www.usb.org/developers/data/otg1</a> 0.pdf

- □ USB 2.0 specification, URL Link: <a href="http://www.usb.org/developers/data/usb\_20.zip">http://www.usb.org/developers/data/usb\_20.zip</a>

- □ USB On-The-Go Marketing Overview, Feb 26, 2002. URL Link: <a href="http://www.usb.org/data/developers/otg/presentations/london/OTG">http://www.usb.org/data/developers/otg/presentations/london/OTG</a> marketing.pdf

# **Ordering information**

| Silicon/Boards | Pin/Ball Number | Package Type | TransDimension Order<br>Number |

|----------------|-----------------|--------------|--------------------------------|

| OTG243 Silicon | 100             | LQFP         | TDOTG243-000C                  |

|                | 84              | TF-BGA       | TDOTG243-00BC                  |

| EVB243 Board   |                 |              | TDOTG243-1070                  |

| BGA243 Board   |                 |              | TDOTG243-1150                  |

| PCE243 Board   |                 |              | TDOTG243-1100                  |

| TransDimension Developer Kits                                  | Platform Vendor        | TransDimension Order<br>Number |

|----------------------------------------------------------------|------------------------|--------------------------------|

| OTG243 / Intel XScale (PXA250) / WinCE.NET                     | Accelent Systems Inc.  | TDOTG243-3010                  |

| OTG243 / Intel XScale (PXA250) / Linux (2.4.18-rmk3-pxa2-asi1) | Accelent Systems Inc.  | TDOTG243-3020                  |

| OTG243 / Intel StrongARM SA1110 / WinCE.NET                    | Accelent Systems Inc.  | TDOTG243-3090                  |

| OTG243 / Intel StrongARM SA1110 / WinCE 3.0                    | Accelent Systems Inc.  | TDOTG243-3030                  |

| OTG243 / Intel StrongARM SA1110 / Linux (2.4.4-rmk3-np1-asi1)  | Accelent Systems Inc.  | TDOTG243-3050                  |

| OTG243 / Intel StrongARM SA1110 / WinCE.NET                    | Intrinsyc IncCerfPDA   | TDOTG243-3100                  |

| OTG243 / Intel StrongARM SA1110 / WinCE 3.0                    | Intrinsyc IncCerfPDA   | TDOTG243-3040                  |

| OTG243 / Intel StrongARM SA1110 / Linux (2.4.9-ac10)           | Intrinsyc IncCerfPDA   | TDOTG243-3060                  |

| OTG243 / Motorola ColdFire 5272/ uCLinux (2.4.17-uc0)          | Arcturus Networks Inc. | TDOTG243-3070                  |

| OTG243 / Sharp LH79520 ARM720T / Linux (2.4.17-rmk2-lineo5)    | SHARP                  | TDOTG243-3080                  |

For additional information, contact your TransDimension Sales Representative or the following:

INTERNET: <a href="http://www.transdimension.com">http://www.transdimension.com</a>

EMAIL: <u>sales@transdimension.com</u>, <u>techsupport@transdimension.com</u>

Headquarters: TransDimension Inc., 2 Venture, Irvine, CA 92618. Tel. (949) 727-2020, FAX (949) 727-3232

Pete Todd, VP of Worldwide Sales,  $\underline{\text{ptodd@transdimension.com}}$

Americas TransDimension Inc., 815 West Market St., Suite 804, Louisville, KY 40202 **Tel. (502)992-3226**, FAX (949) 727-3232

Larry Hayden, e-mail: <a href="mailto:lhayden@transdimension.com">lhayden@transdimension.com</a>

Japan: TransDimension Inc., OYA Bldg. 5, 3 Chome-9-6, Nishishinjuku, Shinjuku-ku, Tokyo, Japan. Tel. +81 (3) 5308 7525, FAX +81 (3) 5308 7526

Masanori Sugane, e-mail: <a href="mailto:sugane@alto.ocn.ne.jp">sugane@alto.ocn.ne.jp</a>

Europe: TransDimension Inc., 7 The Orchard, Hilton, Derbyshire, UK, DE65 5JF. Tel. +44 1283 730045, FAX +44 1283 730651

$\label{lem:new_problem} \textbf{Neil Huntingdon, e-mail:} \ \underline{\textbf{nhuntingdon@transdimension.com}}$

Asia (excluding Japan): TransDimension Inc., 3 Ubi Ave. 3, #05-01, Crocodile House, Singapore, 408857 Tel: +65 6743 9179, Fax: +65 6741 4393

T.L. Nge, e-mail: <a href="mailto:tlnge@transdimension.com">tlnge@transdimension.com</a>

WorldWide Reps.: See detailed listing for your area TransDimension representative by viewing <a href="http://www.transdimension.com">http://www.transdimension.com</a>

THE DEVICE AND ITS DOCUMENTATION ARE PROVIDED "AS IS". TRANSDIMENSION HEREBY DISCLAIMS ALL WARRANTIES, EXPRESS, STATUTORY AND IMPLIED, APPLICABLE TO THE SOFTWARE AND ITS DOCUMENTATION AND ANY RELATED PRODUCTS, INCLUDING, BUT NOT LIMITED TO, ANY WARRANTY OF MERCHANTABILITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE. TRANSDIMENSION ASSUMES NO LIABILITY FOR ANY ACT OR OMISSION OF LICENSEE. IN NO EVENT SHALL TRANSDIMENSION BE LIABLE FOR DIRECT, SPECIAL, INDIRECT, INCIDENTAL, PUNITIVE, EXEMPLARY OR CONSEQUENTIAL. DAMAGES, INCLUDING, WITHOUT LIMITATION, LOSS OF PROPITS OR REVENUE, LOSS OF PRODUCTS, DATA OR ANY ASSOCIATED EQUIPMENT, COST OF CAPITAL, COST OF SUBSTITUTED EQUIPMENT OR PARTS, FACILITIES OR SERVICES, DOWN-TIME OR LABOR COSTS, EVEN IF TRANSDIMENSION HAS BEEN ADVISED OF THE POSSIBILITY THEREOF. The device and any related products are not designed, authorized, or warranted to be suitable for use in life-support devices or systems or other critical applications. Any such use and suddequent liabilities that may arise from such use are totally the responsibilities of the Licensee. Copyright © 2002, TransDimension Inc., All rights reserved. All product names are trademarks or registered trademarks of their respective owners. This document is subject to change without notice.

All Rights Reserved Printed in U.S. September 24, 2002 MU2002, Rev. 1.7